LVDC: A Revolução Silenciosa na Distribuição de Energia para Data Centers e Edifícios - Energia

Fabio 15 Nov 2025 energia e ciênciasLVDC: A Revolução Silenciosa na Distribuição de Energia para Data Centers e Edifícios

A forma como distribuímos energia elétrica está passando por uma transformação fundamental. Enquanto a corrente alternada (AC) dominou por mais de um século, a corrente contínua de baixa tensão (LVDC - Low Voltage Direct Current) emerge como uma solução superior para as demandas energéticas do século XXI, especialmente em data centers, edifícios inteligentes e instalações industriais.

O Contexto: Por Que Mudar Agora?

Data Centers e o Consumo Global de Energia

Os data centers consomem mais de 200 TWh por ano, representando cerca de 1% da demanda global de eletricidade. Com o crescimento exponencial da inteligência artificial e computação em nuvem, essa demanda só tende a aumentar. Os custos de energia dominam os custos totais do ciclo de vida dessas instalações, tornando a eficiência energética não apenas uma questão ambiental, mas também econômica.

O Desafio das Arquiteturas Tradicionais

Os racks atuais em data centers de IA dependem de distribuição de energia a 54 VDC, onde barras de cobre volumosas transportam eletricidade das prateleiras de energia montadas em rack para as bandejas de computação. À medida que os racks excedem 200 quilowatts, essa abordagem começa a atingir limites físicos.

O problema se torna ainda mais crítico: a física do uso de 54 VDC em um único rack de 1 MW requer até 200 kg de barra de cobre, e as barras de rack sozinhas em um único data center de 1 gigawatt poderiam requerer até meio milhão de toneladas de cobre.

LVDC: A Solução Emergente

O Que É LVDC?

LVDC refere-se a sistemas de distribuição de energia em corrente contínua operando em tensões tipicamente entre 48V e 1500V. Esses sistemas representam uma mudança de paradigma em relação às arquiteturas AC tradicionais, oferecendo múltiplas vantagens em eficiência, densidade de potência e integração com fontes renováveis.

Níveis de Tensão Padronizados

Os sistemas Current/OS suportam tensões nominais de 48V DC, 175V DC, 350 VDC e 700 VDC em sistemas unipolares, e 350/700 VDC e 700/1400V DC em sistemas bipolares. Cada nível de tensão é adequado para aplicações específicas:

- 48 VDC: Sistemas locais pequenos como PoE, USB-C ou aplicações de iluminação

- 350 VDC: Instalações onde tradicionalmente seria usado AC monofásico de 230V

- 700 VDC: Instalações de alta potência ou circuitos de distribuição

- 800 VDC: O novo padrão emergente para data centers de IA

A Arquitetura 800 VDC da NVIDIA

Transformando Data Centers de IA

A NVIDIA está liderando a transição para infraestrutura de energia de data center a 800 VDC para suportar racks de TI de 1 MW e além, começando em 2027. Esta iniciativa representa uma mudança fundamental na forma como alimentamos instalações de computação de alto desempenho.

Benefícios Quantificáveis

A arquitetura 800 VDC oferece vantagens impressionantes:

Melhoria de até 5% na eficiência energética de ponta a ponta em comparação com sistemas de 54V atuais

Custos de manutenção reduzidos em até 70% devido a menos falhas de PSU e menores custos de mão de obra para manutenção de componentes

Menores despesas de resfriamento pela eliminação de PSUs AC/DC dentro dos racks de TI

Redução de 45% nos requisitos de cobre, com a capacidade de transmitir 85% mais potência através do mesmo tamanho de condutor

Como Funciona

Ao converter energia da rede AC de 13,8 kV diretamente para 800 VDC no perímetro do data center usando retificadores de grau industrial, a maioria das etapas de conversão intermediárias são eliminadas. Esta abordagem simplificada minimiza perdas de energia.

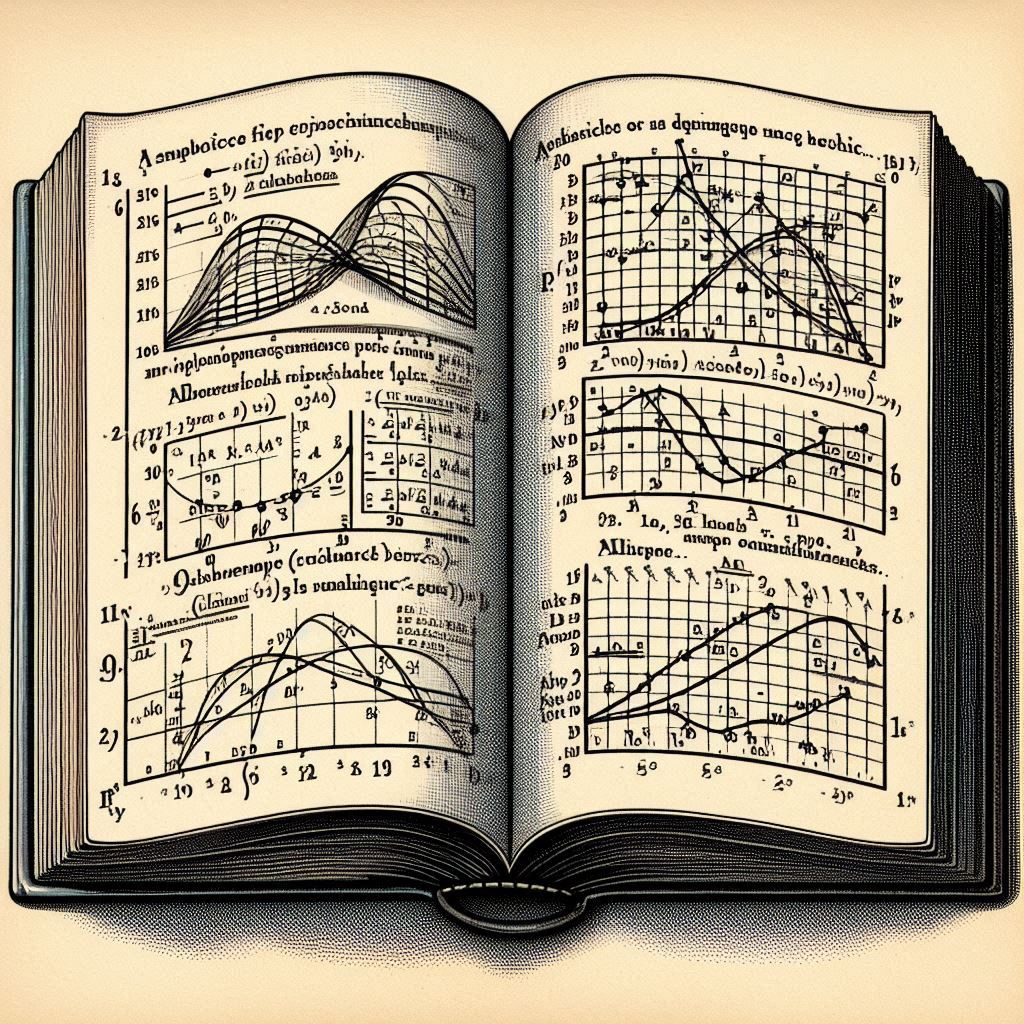

Comparação: AC vs. DC na Distribuição

Eficiência no Mundo Real

A distribuição AC tradicional a 400V atinge uma eficiência total de aproximadamente 97,1% do MVAC até a entrada da conversão DC-DC de 400V/48V no nível do rack.

Aumentando a tensão de distribuição para 690V AC, a eficiência aumenta para aproximadamente 97,8%.

Com distribuição DC, os ganhos são ainda mais significativos:

Um sistema de ±400V DC alimentado por fontes DC (células de combustível, baterias, PV) atinge uma eficiência total de aproximadamente 98,7%

Quando alimentado pela rede, um sistema de ±400V DC com retificador PFC SiC centralizado alcança aproximadamente 97,9% de eficiência

Redução nas Perdas de Distribuição

Usando a mesma barra condutora em configuração AC ou DC, a mudança de 400V AC para 800V DC (±400V DC) resulta em redução de 75% nas perdas de distribuição ou 75% na massa de cobre.

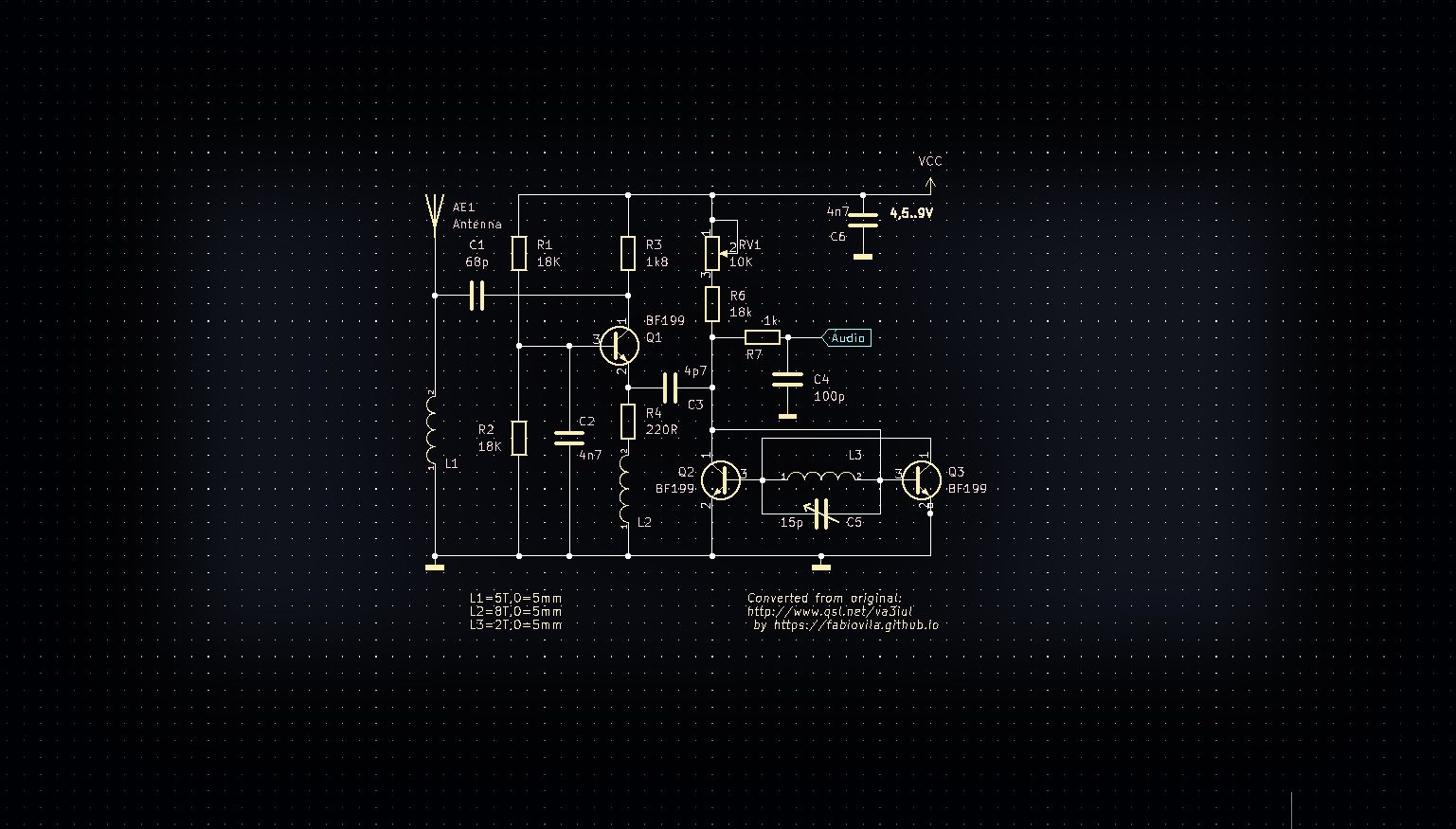

Interfaces MVAC-LVDC: Conectando Redes à Distribuição DC

Transformadores Híbridos

Os transformadores híbridos MVAC-LVDC utilizam processamento parcial de potência em modo comutado, com módulos de filtro ativo (AF) com aproximadamente 25% da potência nominal para garantir correntes senoidais na rede e compensação de potência reativa.

Esta solução alcança eficiência de aproximadamente 98,5% com densidade de potência de cerca de 0,2 kW/dm³.

LFT + Retificador PFC SiC Central

Uma solução utilizando retificador PFC centralizado com tecnologia SiC de 1200V e transformador seco/EcoDesign de alta eficiência oferece funcionalidade completa (potência reativa, fluxo de potência bidirecional), alta robustez, baixa complexidade e escalabilidade para níveis MVAC mais altos.

Esta configuração atinge eficiência de aproximadamente 98,2% com densidade de potência de cerca de 0,25 kW/dm³.

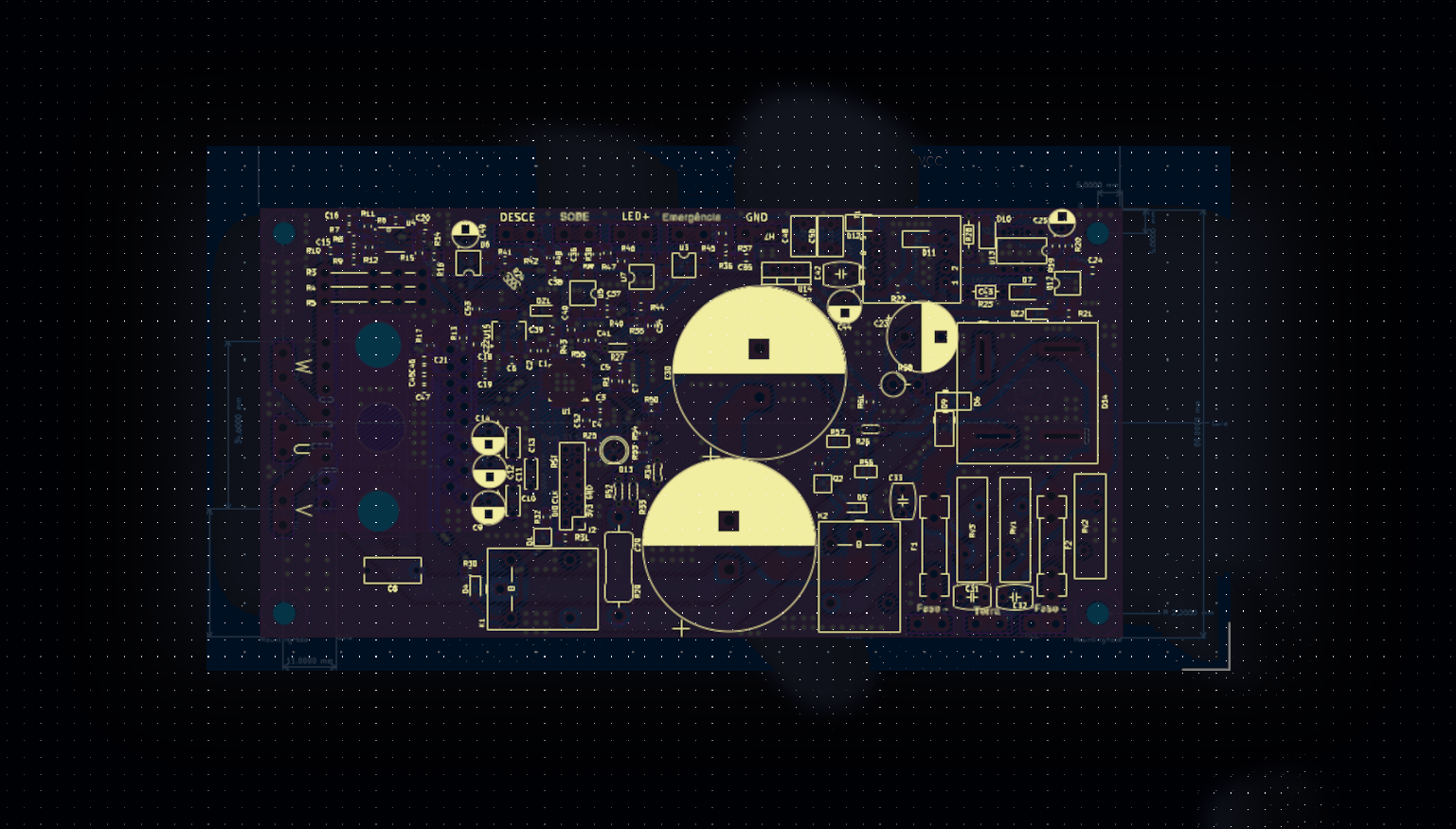

Current/OS: Um Padrão Aberto para LVDC

O Que É Current/OS?

Current/OS é um conjunto evolutivo de regras para garantir interoperabilidade, segurança, escalabilidade, efetividade e confiabilidade de instalações elétricas DC prosumer com fontes distribuídas. Estas regras definem todos os aspectos do sistema para cargas, fontes e cabos.

Bandas de Tensão Inteligentes

Um dos conceitos mais inovadores do Current/OS é o uso de bandas de tensão para controle distribuído sem necessidade de comunicação central:

Dentro das bandas nominais, a tensão é usada como um sinal para comunicar a disponibilidade de energia às cargas e fontes conectadas à rede, fazendo-as reagir de acordo.

As bandas incluem:

- Banda de blackout (B1): Sistema desligado, requer reinicialização

- Banda de emergência (B2): Potência disponível apenas suficiente

- Banda nominal (B3): Operação normal

- Banda de sobretensão (B4): Condições temporárias

- Bandas de proteção (B5-B7): Ativação de dispositivos de proteção

Zonas DC para Segurança

Para facilitar o projeto e operação de instalações DC, circuitos ou grupos de circuitos são classificados de acordo com a energia de falta disponível e os meios de proteção em 6 Zonas DC, rotuladas como 0, 1, 2.1, 2.2, 3 e 4.

Zona DC 3 é particularmente interessante para distribuição: Múltiplas fontes distribuídas com OCPD tendo tempo de interrupção menor que 10 μs resultam em correntes de falta ultra-limitadas no barramento DC, permitindo que as fontes sejam distribuídas e mantendo a energia incidente sempre muito pequena.

Suporte da Indústria

ABB e a Arquitetura 800 VDC

A multinacional sueco-suíça ABB anunciou uma parceria com a Nvidia que verá seu suporte ao lançamento da arquitetura de energia 800 VDC da Nvidia para racks de servidor de 1 megawatt.

Por mais de uma década, a ABB tem estado na vanguarda da inovação LVDC, fornecendo tecnologias habilitadoras nos setores marítimo, de carregamento de veículos elétricos, industrial e de edifícios.

Experiência Marítima

Desde 2013, embarcações marítimas usam sistemas LVDC com 1000 VDC e até 20 MW, relatando economia de energia de 20-40% e custos de manutenção até 30% menores.

Ecossistema de Parceiros

A NVIDIA está colaborando com parceiros-chave da indústria em todo o ecossistema elétrico de data center, incluindo fornecedores de silício como Analog Devices, Infineon, Innoscience, MPS, Navitas, OnSemi, Renesas, ROHM, STMicroelectronics e Texas Instruments.

Desafios e Considerações

Proteção e Segurança

A distribuição DC apresenta desafios únicos de proteção. Os requisitos de proteção têm impacto significativo no dimensionamento da eletrônica de potência do lado MV dos SSTs.

A solução está em disjuntores semicondutores ultrarrápidos e sistemas de proteção inteligentes que podem detectar e isolar faltas em microssegundos.

Corrosão

Correntes de fuga DC podem ter efeito prejudicial sobre o aço de reforço no concreto dos edifícios. Apenas alguns miliamperes de correntes de fuga já podem causar sérios problemas de corrosão.

A solução inclui o uso de aterramento TN-S e dispositivos de substituição de célula de polarização (PCR) com diodos para prevenir correntes de fuga DC.

Padronização

Embora existam avanços significativos, a padronização completa ainda está em desenvolvimento. Organizações como IEC, Current/OS Foundation e grupos industriais estão trabalhando ativamente para estabelecer padrões globais.

Aplicações Além dos Data Centers

Edifícios Inteligentes

Sistemas DC de 350V são recomendados para instalações onde AC monofásico de 230V seria tipicamente usado, por exemplo, para residências ou usos similares.

Integração de Renováveis

A distribuição DC aproveita a saída DC de células de combustível, baterias e sistemas fotovoltaicos, eliminando uma etapa de conversão DC/AC adicional.

Infraestrutura de Recarga de VEs

A experiência com carregadores rápidos DC para veículos elétricos está contribuindo significativamente para o desenvolvimento de padrões e componentes para distribuição LVDC em edifícios.

O Futuro da Distribuição de Energia

Timeline de Implementação

A produção em escala total de data centers 800 VDC coincidirá com os sistemas rack-scale NVIDIA Kyber em 2027, garantindo escalabilidade perfeita para modelos de IA cada vez mais exigentes.

Impacto Econômico

À medida que as cargas de trabalho de IA requerem 100x a 1.000x mais computação por consulta, esta arquitetura permite crescimento sustentável enquanto reduz o custo total de propriedade (TCO) em até 30% através de ganhos em eficiência, confiabilidade e melhorias na arquitetura do sistema.

Sustentabilidade

Transformadores de baixa frequência têm vida útil típica de mais de 40 anos, comparado a aproximadamente 10 anos para SSTs, além de vantagem de reciclabilidade de LFTs e unidades de alta potência.

Conclusão

LVDC não é apenas uma tendência tecnológica passageira, mas uma evolução fundamental na forma como distribuímos e utilizamos energia elétrica. Com benefícios comprovados em eficiência, redução de custos, facilitação de energias renováveis e preparação para as demandas futuras de computação de alto desempenho, LVDC está posicionado para se tornar o padrão dominante em data centers, edifícios inteligentes e instalações industriais nas próximas décadas.

Enquanto 690V AC é competitivo com ±400V DC, considerações adicionais sobre integração de renováveis, energia de backup de células de combustível e serviços de rede favorecem as soluções DC.

A transição já começou. Com o suporte de gigantes da indústria como NVIDIA, ABB e um ecossistema crescente de fornecedores, LVDC está pronto para revolucionar a infraestrutura energética do século XXI, tornando-a mais eficiente, sustentável e preparada para o futuro.

Referências: Este artigo foi baseado em publicações técnicas de ETH Zürich, NVIDIA, ABB e documentação Current/OS Foundation, representando o estado da arte em sistemas LVDC até 2025., R., Popp, M., & Schaefer, M. (2024). “Dynamic modeling, design and simulation of a thermal pumped piston storage within a renewable energy distribution system.” Journal of Energy Storage, 100, 113348. https://doi.org/10.1016/j.est.2024.113348